从手机多摄像头、车载屏幕、到嵌入式 AI 终端,为什么这些设备能做到 “看得清,显得快”?

—— MIPI D-PHY

MIPI D‑PHY 是由 MIPI Alliance 定义的高速串行物理层接口,广泛用于 Camera Serial Interface (CSI‑2)、Display Serial Interface (DSI) 以及其他需要高速/低功耗传输的场景。它采用源同步(source‑synchronous)的差分信号结构,具备 低功耗(LP)与 高速(HS) 两种工作模式,能够在同一根 lane 上实现双向或单向传输。

Display Serial Interface (DSI)

DSI 是 MIPI Alliance 定义的高速串行显示接口,用于主机处理器(Host)与 显示模块(Display)之间的通信。它基于 MIPI D‑PHY(或 C‑PHY)物理层,实现 差分信号传输,能够在少量引脚上提供 高带宽、低功耗 的显示数据通路。

架构层次

应用层:定义图像格式、虚拟通道(VC)等。

协议层:封装为 Long Packet(图像数据)和 Short Packet(控制/状态)并支持 Escape Mode、ULPS 等低功耗模式。

物理层:使用 MIPI D‑PHY(或 C‑PHY)提供Clock lane+1~4(甚至8)Data lane 的差分信号。

关键技术参数

标准版本:目前主流实现遵循 MIPI CSI‑2 v1.3,最新的 v2.0 已在部分高端 SoC 中出现(如 RK3576系列)。

Lane 数量:1、2、4、8 lane 可选,常见 2‑lane(移动终端)或 4‑lane(高分辨率相机)配置。

速率:

HS(High‑Speed)模式下 每 lane 2.0 ~ 2.5 Gbps(v1.3);

v2.0 规范支持 最高 3.5 Gbps/ lane,4 lane 合计可达 10 Gbps。

像素吞吐:2 lane 2.5 Gbps 可实现 200 Mpixels/s(RGB888)、333 Mpixels/s(Raw10)。

数据格式:支持 RAW8/10/12/14、RGB565/888//YUV422/420等全部 MIPI CSI‑2 标准定义的格式。

虚拟通道:最多 8 VC(v2.0)或 4 VC(v1.3),可在同一链路上复用多路图像或元数据。

低功耗模式:LP、Escape、ULPS 均在协议层定义,用于待机或控制指令传输。

常见芯片

RK3576:

Support 3 MIPI CSI-2 interfaces

Two 4 data lanes of D-PHY v1.2

Each interface may be configured as 2x2 data lanes port.

One 4 data lanes (or 3 data trios) of C/D-PHY

D-PHY is v2.0 which lane speed is 4.5Gbps

RK3588:

TWO MIPI DC(DPHY/CPHY) combo PHY

Support to use DPHY or CPHY

Each MIPI DPHY V1.2, 4lanes, 2.5Gbps per lane

Camera Serial Interface (CSI‑2)

CSI‑2 是由 MIPI Alliance 制定的摄像头高速串行接口,用于在相机传感器与主处理器/ISP/FPGA 之间传输 RAW、YUV、RGB 等图像数据。采用差分串行传输(基于 D‑PHY 或 C‑PHY),能够实现高分辨率‑高帧率的图像流。

体系结构

PHY 层:差分链路与时钟

差分阻抗与信号完整性,每条lane需保持 100 Ω ±20% 的差分阻抗,并端接100Ω电阻,以防止信号反射,保障高速信号质量。

HS/LP双模式切换

支持高速(HS)与低功耗(LP)模式。严格的切换时序 (LP-11 → LP-01 → LP-00 → HS-EN) 是避免总线冲突的关键。

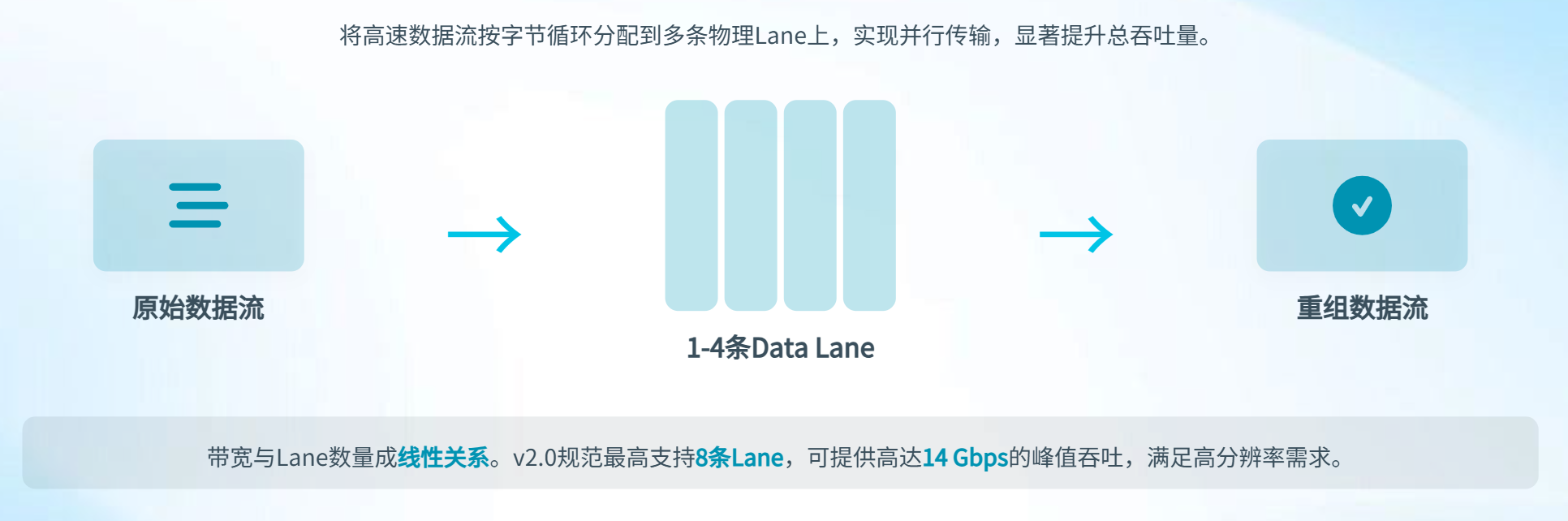

Lane 管理层:数据拆分与重组

将高速数据流按字节循环分配到多条物理Lane上,实现并行传输,显著提升总吞吐量。

Protocol 层:长短包结构

Application 层:像素格式与DCS

关键技术参数

Lane 数量:1、2、4(常规)或 8(高端)条 Data lane,Clock lane 为单向

速率:

v1.3 规范:每 lane 2.0 ~ 2.5 Gbps;v2.0(2024‑2025)提升至 3.5 Gbps/ lane,4 lane 可达 ≈14 Gbps

像素吞吐:2 lane 2.5 Gbps 可实现 200 Mpixels/s(RGB888)、333 Mpixels/s(RAW10)

虚拟通道:v1.3 支持 4 VC,v2.0 扩展至 8 VC,允许同一链路上多路显示或元数据并行传输

数据格式:支持 RGB565/888、YUV422/420、RAW8/10/12/14 等多种像素格式

压缩:支持 VESA DSC(Display Stream Compression),可在 4K/60 Hz、8K/30 Hz 场景下进一步降低带宽需求