超微缩和3D集成共同推动工艺前进

2020-12-23 17:57:39

摩尔定律的未来还看不到尽头,这是台积电中国副总裁陈平博士最近在演讲中传递的观点。

摩尔定律到底有没有到尽头,这是一个业界争议了二十多年的话题,如果但从半导体工艺制程的进展上看,摩尔定律依旧继续前行。作为目前半导体制造领域的领导者,来自台积电的陈平博士就摩尔定律的发展进行了分析,本文观点性内容节选自陈平博士在ICCAD活动的现场报告。

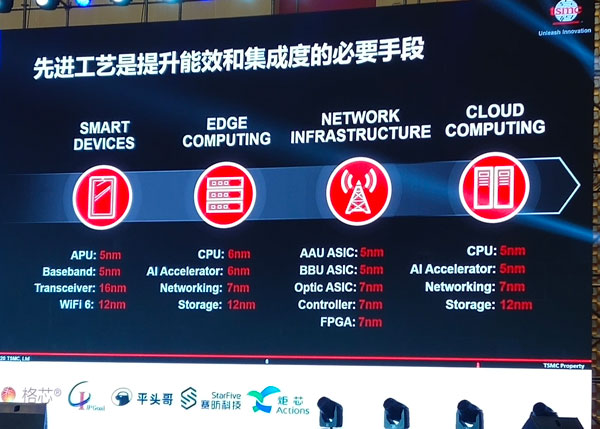

计算是整个电子产业的核心驱动力,两年前在珠海的设计年会上,当年的预测移动计算跟普及计算的两个交差点会发生在2020年,从今年的产品来看,这一点真实发生了。所谓普及计算的时代,意味着计算平台会从移动的智能手机,演变成多个平台,包括移动平台、高速计算平台,IoT平台和智能车载平台。在新的时期里的核心技术是5G和AI,5G是代表了连接技术,AI是数据的处理技术。5G跟AI非常依赖工艺技术之上,所以它对性能、功耗和集成度的要求都非常高。

在工艺上满足要求无非是两个路径,第一个路径是继续延伸所谓的摩尔定律,就是微缩技术,所以在单片上面按照原来摩尔定律的方向继续延伸。另外一个路径是实现3D集成,目前台积电在两个方面都取得了很好的成果,目前世界上最大的GPU SoC,已经有了500亿晶体管,而用3D集成现在做到了最大的芯片是有2000亿。

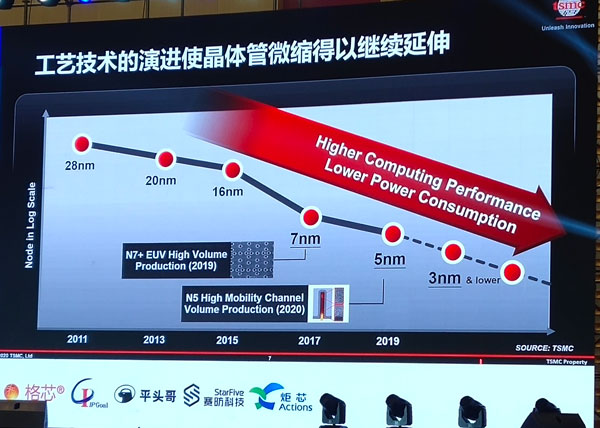

5G和AI共同的要求是两个,一个是高能效,不管你是移动终端还是云计算,都需要很高的能效。第二个是集成度,要把更多的晶体管放在系统芯片里面去。满足这两个要求,先进工艺是不二选择,必须有先进工艺来支撑这件事。我们看一下工艺,我们的工艺能不能支持这样的应用要求呢,这个曲线是我们熟悉的,所谓摩尔定律的一个曲线。5纳米今年台积电进入了大量的量产,已经有三个机种的量产。5纳米比7纳米还是更顺利。5纳米做的很多的器件,比如说苹果12,很多朋友都在享用。3纳米的研发进展现在也很顺利,所以台积电应该是按照我们的计划在进行,明年可以做完认证,后年会有大量的量产。5纳米已经被证明是成功的,再往前走,我们的工艺到底能够走多远呢,我跟大家做一些简单的分析。

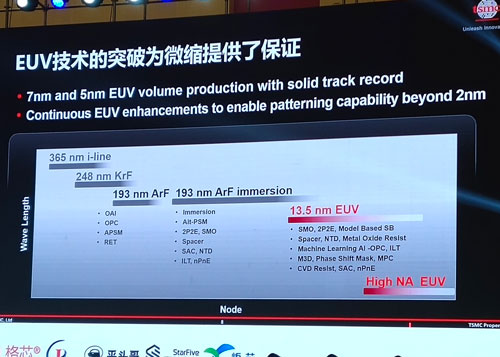

我们知道做晶体管的微缩有几个大的技术,第一个就是光刻技术,基于可见光的光刻技术,很多年一直用各种各样的弥补方法,终于在两年前我们的EUV技术成熟,进行量产。它的光波长是13.5纳米。我们的日子就比以前好过了很多,所以7nm和5nm这两代已经非常成功的引进,量产环节上已经做得非常好了。

再往前这个研发还在继续的进行,所以EUV还会得到不断的扩展,下一个节点叫high NA EUV。为了晶体管微缩,不光要保证光刻的技术,你还要保证器件结构和器件材料,因为当你器件变得很小的时候,你的器件结构就不能支持你的电性要求。从10纳米开始转换,已经用了好几代,一直从3纳米的结构都是可以支持的。3纳米以后需要做器件结构的一些改变,现在这方面也有很好的候选者,这些都是后面的,所以在器件结构上,后面也是有准备的。

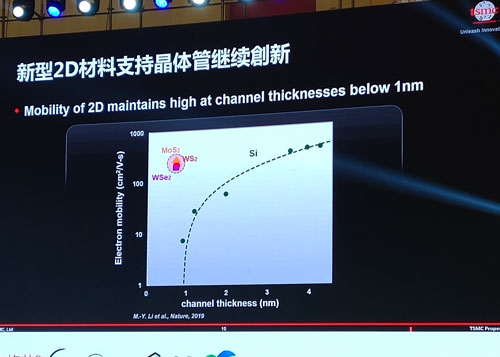

还有一个材料,这张图可以显示,如果用纯粹的微材料的话,到3纳米以后,你的速度会快速的降低。好在我们人类的创新从来没有停止,前几年又有科技人员,又创造出了新的2D的材料,这些材料就是图中所标识,他又可以拉回到水平去。所以摩尔定律,什么时候终结没有答案,因为就我个人来说,我第一次参加这个讨论是30年前,最近的20年每年都有人在非常确定的说,但是我们永远不能低估人类的创造力和创新,当我们遇到一个困难的时候,总有优秀的科学家两找到新的答案。

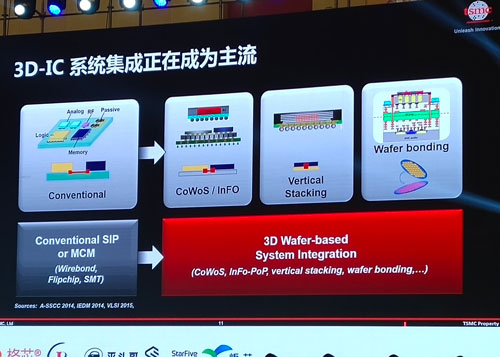

刚才讲的是我们的单片上集成的晶体管,与此同时大家都已经注意到所谓3DIC,就是异构或者同构的集成,最近已经成为了我们行业的主流。从需求上来讲有两个很大的推手要我们做这件事。第一件事,我们在谈SoC的时候,知道各种工艺技术它的路径是不一样的。我们的存储器就比它要慢得多。在5纳米以后明显放慢,还有一些特殊工艺,像射频工艺,他们那些本来就很慢,如果你把所有的东西都集成在同一个芯片上,第一不是永远可能,第二也不经济,所以现在更好的方式,异构的集成来做,这是一个必须要做的事,也是摩尔定律延伸的另一个手段。

第二是同构的,我们需要把很多的晶体管放在电路上去,但是受光刻的限制,830平方毫米左右,这个是受限的。你如果做七八百个平方,你的成本,封装,各种问题就会出现,所以我们会把一个大的分成几个小的,然后做到一起。

台积电在这方面过去十来年,一直致力于研究,因为我们早就预见这种需求,一直在做研究,我们现在已经推出了,最后称之为3D这一个平台,在3D平台里面大概分两大类的工艺,这个平台类涵盖的工艺细节非常多。

总体来说分两个部分,第一个部分叫做前段3D,这个是他对工艺的要求是最高的。第二种所谓的先进封装的方式,这种有代表性的,我们台积电已经做了七八年的,CoWos技术和info技术,和传统的是相辅相成的,鼓励大家对这个方面多关注。

除了我刚才讲的3D,在晶体管的技术微缩以外,也除了我刚才已经提到的3D集成以外,还有一个重要的趋势,就是设计和工艺的紧密结合,这个词不是一个很虚幻的词,现在所有的工艺开发和设计的一个非常重要的元素。在系统架构上,设计的时候跟硬件之间的结合也必须纳入一个考虑,所以软件和硬件的协同设计,协同优化是一个系统设计的必须。

所以总结刚才的分析,以集成电路纯技术的发展方向来看,我们的看法是晶体管的技术微缩,3D的集成,软硬件的协同优化,这三个是我们的三大元素,缺一不可,指导我们今后很多年的发展。